前言:Pcie3.0x4 眼图测试 物理层一致性测试

Pcie3.0x4 眼图测试 物理层一致性测试

下面是一个 DDR3 设计的实际案例。按照传统的方式进行设计时,工程师会按照主芯片给的设计规范进行设计。结合项目工程的需要,其 DDR3 的采用的是 T 型的拓扑结构, ECC 放置在如下图 5 圆圈中所示位置。在生产完成后的调试过程中,发现 DDR3 的信号出现非单调性。

图 5 DDR3 T 型结构(ECC 放在中间位置)

图 6 DDR3 T 型结构(ECC 放在中间位置)的仿真波形

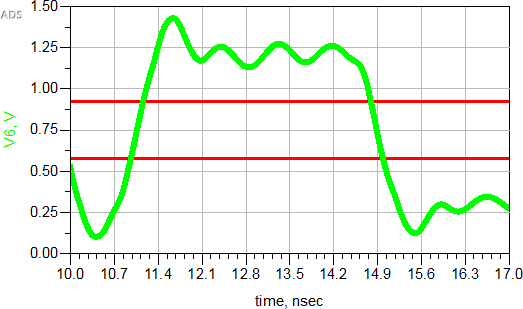

在 ADS 中搭建拓扑结构并仿真,获得仿真结果如下图 6 所示,与测试结果基本吻合。

显然,所获得的波形有一个比较明显的非单调,不满足信号质量的要求,在信号传输过程中就有可能产生误码。通过分析,把ECC 的位置调整到如下图 7 所示的圆圈处:

图 7 DDR3 T 型结构(ECC 放置在T 型结构的一侧)

同样,在 ADS 中仿真的结果如下图 8 所示: